时序逻辑电路

Sequential Logic Circuit 时序逻辑电路

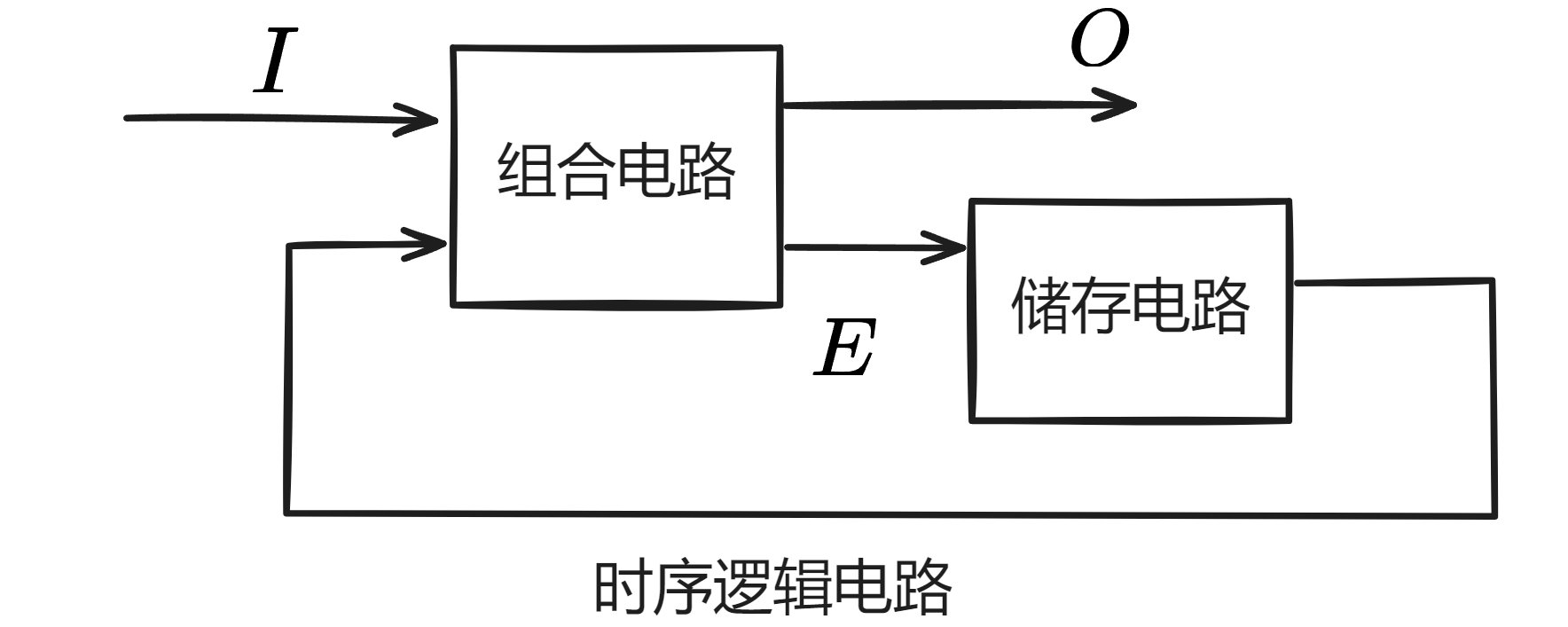

时序逻辑电路是一种数字逻辑电路,其输出不仅取决于当前的输入信号,还取决于电路在过去时刻的状态。这意味着时序逻辑电路具有记忆功能,能够存储信息,因此它也被称为“带记忆的逻辑电路”。时序逻辑电路是构建寄存器、计数器、状态机和存储器等复杂数字系统的基础。

一、基本构成与特性

时序逻辑电路通常由两大部分组成:

- 组合逻辑电路:负责根据当前输入和电路的当前状态(反馈信号)产生激励信号和输出信号。

- 储存逻辑电路 (记忆元件):通常由触发器组成,用于存储电路的当前状态。触发器在时钟脉冲的控制下改变状态,并将状态信息反馈给组合逻辑电路。

特性:

- 记忆性:能够存储信息,其输出依赖于历史输入序列。

- 反馈:记忆元件的输出(状态信号)会反馈到组合逻辑电路的输入端,影响激励信号的产生。

- 时钟控制:大多数时序逻辑电路是同步的,状态变化发生在时钟脉冲的特定边沿。

二、数学描述与方程组

- 输入信号:

- 输出信号:

- 激励信号:

(由组合逻辑电路产生,驱动记忆元件) - 状态信号/状态变量:

(记忆元件的输出,代表电路的当前状态)

时序逻辑电路的行为可以用一组逻辑方程来描述:

其中,

三、分析方法

分析时序逻辑电路的目的是理解其功能,即在给定输入序列的情况下,电路如何从一个状态转换到另一个状态,并产生相应的输出。

- 写出激励方程和输出方程:根据电路图,写出组合逻辑部分的激励信号和输出信号与输入信号和状态信号之间的逻辑关系。

- 写出状态转换方程:根据所使用的触发器的特性方程,结合激励方程,写出电路的次态(

)与现态( )和输入(I)之间的关系。 - 列出状态转换表:根据状态转换方程,列出所有可能的现态和输入组合,以及对应的次态和输出。这是描述时序逻辑电路行为最完整的方式。

- 绘制状态转换图:将状态转换表中的信息以图形化的方式表示出来。每个状态用一个圆圈表示,状态之间的转换用带箭头的弧线表示,弧线上标注输入/输出。

- 绘制时序图:根据特定的输入序列,绘制出电路中关键信号(输入、状态、输出、时钟)随时间变化的波形图,直观地展示电路的时序行为。

四、设计方法

设计时序逻辑电路的目的是根据给定的功能要求,构建出相应的电路。

- 抽象状态:根据功能要求,定义电路可能处于的所有状态,并进行状态编码(将抽象状态映射为二进制状态变量)。

- 建立状态转换图/表:根据功能要求,绘制出电路的状态转换图或列出状态转换表,明确每个状态在不同输入下的次态和输出。

- 选择触发器类型:根据设计需求(如速度、功耗、成本等)选择合适的触发器类型(如 D 触发器、JK 触发器等)。

- 求激励方程和输出方程:根据状态转换表和所选触发器的特性,利用卡诺图或其他化简方法,求出激励信号和输出信号的逻辑表达式。

- 绘制逻辑图:根据激励方程和输出方程,使用逻辑门电路和触发器符号绘制出最终的电路图。

- 检查与验证:对设计好的电路进行仿真或实际测试,确保其满足所有功能要求。

五、时序逻辑电路的应用

时序逻辑电路是数字系统中的核心组成部分,广泛应用于: